8.1 Adding Power Losses to a Testplan

The built-in efficiency testplan measures the overall efficiency of the converter. In this section, you learn how to make the following additions to the built-in efficiency testplan:

- Add individual power losses to the report so you can observe how the power losses vary over line and load changes.

- Separate the gate-drive power loss from the input source power of the circuit.

This example generates five graphs:

- Total switching losses for the MOSFET in a sync buck circuit

- Total conduction losses for the MOSFET in a sync buck circuit

- Overall efficiency

- Gate-drive power loss

- Remaining losses in the circuit Note: To plot the remaining power losses, you will use a feature of the CreateXYScalarPlot() function to plot mathematical expressions of measured scalar values.

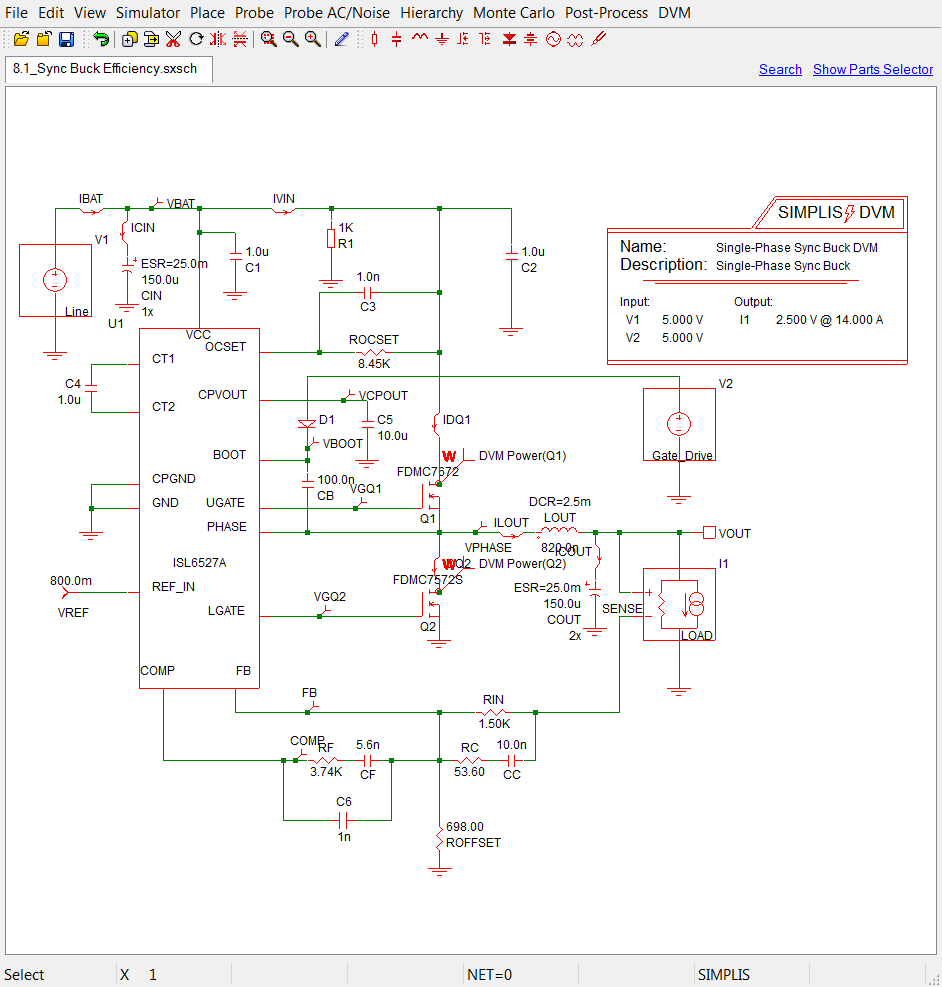

This example is based on a new schematic that uses discrete packaged MOSFETs that allow the MOSFET losses to be measured directly. The efficiency and power-loss schematic shown below is available from SIMPLIS_dvm_tutorial_examples.zip at this path: ISL6527A\8.1_Sync Buck Efficiency.sxsch

When compared with previous schematics, notice the following differences:

- Fixed power probes with the "mean" fixed probe measurement applied have been placed on the MOSFETs Q1 and Q2. These probes generate the scalar values for the total loss in the devices.

- A second input source has been added to supply power to the high-side gate driver. When DVM calculates the efficiency of a circuit, it includes the power from all input sources and all output loads. The individual power delivered by each input source and dissipated by each output load is also measured and reported as a scalar value.

- The names of the sources have been changed to be more descriptive of their function for the following reasons:

- The names for both probes and sources are important because the generated scalar names include those names.

- Since the testplan uses the Alias function to generate unique scalar names, the testplan and schematic must have the same probe, source, and load names. This is important to remember when taking an existing testplan and using it on a new schematic.

This prepared schematic runs exactly like the built-in efficiency testplan.

- The scalar values will be generated by the probes and by DVM.

- Those scalars are then assigned aliases based on the input voltage for the test.

- After all the tests complete, a final test is executed which generates the summary curves. Instead of using the create column to define the CreateXYScalarPlot() curve functions, a final-process script helps make the testplan more manageable. This script is available from SIMPLIS_dvm_tutorial_examples.zip at this path: scripts/8.1_efficiency_and_powerloss_post_process.sxscr

The one portion of this script that needs discussing is the scalar expression capabilities of the CreateXYScalarPlot() function. For example, one of the CreateXYScalarPlot() functions is

Let ignoreme = SimplisDVMAdvancedUtilMeasurementCreateXYScalarPlot(['ILOAD_Nom', 'Power_Line_Nom - Power_Load_Nom - Power_Q1_Nom - Power_Q2_Nom + Power_Gate_Drive_Nom', 'ILOAD_Nom Power_Line_Nom Power_Load_Nom Power_Q1_Nom Power_Q2_Nom Power_Gate_Drive_Nom', 'DVM Vin Nom', 'DVM Remaining Power Loss', 'A1', 'vert', 'xlabel=Load Current xunits=A ylabel=Power Loss yunits=W showpoints=true color=blue'], log_file)

The second argument of this function is the mathematical expression of the remaining power loss once the input line, output load, gate drive, and MOSFET power losses have been removed:

'Power_Line_Nom - Power_Load_Nom - Power_Q1_Nom - Power_Q2_Nom + Power_Gate_Drive_Nom'

This expression is a good example of scalar mathematics that DVM evaluates on a point-by-point basis and then plots the resulting values.

The testplan for this schematic is available from SIMPLIS_dvm_tutorial_examples.zip at this path: testplans/8.1_efficiency_and_powerloss.testplan.

Although this testplan is similar to the built-in efficiency testplan in 5.1 Running the Built-In Efficiency Testplan, it differs in the following ways:

- With the addition of a second input source, you now have two source columns.

- Measurement columns have been added for the scalar aliases.

- On the last line of the testplan is a single FinalProcess entry for the post-process script. with a path relative to the schematic: ..\scripts\8.1_efficiency_and_powerloss_post_process.sxscr

- Additional tests have been added for the lower load currents in order to fill in the efficiency curve points. This testplan uses 5% load steps from 5% to 40% of full load, and 10% load steps from 40% to 100% of full load.

| *** | |||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| *** 8.1_efficiency_and_powerloss.testplan | |||||||||||||

| *** | |||||||||||||

| *?@ Analysis | Objective | Source | Source | Load | Label | Create | Create | Create | Create | Create | Create | Create | FinalProcess |

| *** | |||||||||||||

| *** | |||||||||||||

| Steady-State | Steady-State | SOURCE(INPUT:1, Nominal) | SOURCE(INPUT:2, Nominal) | LOAD(OUTPUT:1, 5%) | Steady-State|Steady-State|Vin Nominal|5% | Alias( Efficiency, Efficiency_nom) | Alias( AVG(ILoad), ILOAD_Nom ) | Alias( AVG(Power(Q1)) , Power_Q1_Nom ) | Alias( AVG(Power(Q2)) , Power_Q2_Nom ) | Alias( Power(Line) , Power_Line_Nom ) | Alias( Power(Load) , Power_Load_Nom ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Nom ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Nominal) | SOURCE(INPUT:2, Nominal) | LOAD(OUTPUT:1, 10%) | Steady-State|Steady-State|Vin Nominal|10% | Alias( Efficiency, Efficiency_nom) | Alias( AVG(ILoad), ILOAD_Nom ) | Alias( AVG(Power(Q1)) , Power_Q1_Nom ) | Alias( AVG(Power(Q2)) , Power_Q2_Nom ) | Alias( Power(Line) , Power_Line_Nom ) | Alias( Power(Load) , Power_Load_Nom ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Nom ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Nominal) | SOURCE(INPUT:2, Nominal) | LOAD(OUTPUT:1, 15%) | Steady-State|Steady-State|Vin Nominal|15% | Alias( Efficiency, Efficiency_nom) | Alias( AVG(ILoad), ILOAD_Nom ) | Alias( AVG(Power(Q1)) , Power_Q1_Nom ) | Alias( AVG(Power(Q2)) , Power_Q2_Nom ) | Alias( Power(Line) , Power_Line_Nom ) | Alias( Power(Load) , Power_Load_Nom ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Nom ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Nominal) | SOURCE(INPUT:2, Nominal) | LOAD(OUTPUT:1, 20%) | Steady-State|Steady-State|Vin Nominal|20% | Alias( Efficiency, Efficiency_nom) | Alias( AVG(ILoad), ILOAD_Nom ) | Alias( AVG(Power(Q1)) , Power_Q1_Nom ) | Alias( AVG(Power(Q2)) , Power_Q2_Nom ) | Alias( Power(Line) , Power_Line_Nom ) | Alias( Power(Load) , Power_Load_Nom ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Nom ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Nominal) | SOURCE(INPUT:2, Nominal) | LOAD(OUTPUT:1, 25%) | Steady-State|Steady-State|Vin Nominal|25% | Alias( Efficiency, Efficiency_nom) | Alias( AVG(ILoad), ILOAD_Nom ) | Alias( AVG(Power(Q1)) , Power_Q1_Nom ) | Alias( AVG(Power(Q2)) , Power_Q2_Nom ) | Alias( Power(Line) , Power_Line_Nom ) | Alias( Power(Load) , Power_Load_Nom ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Nom ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Nominal) | SOURCE(INPUT:2, Nominal) | LOAD(OUTPUT:1, 30%) | Steady-State|Steady-State|Vin Nominal|30% | Alias( Efficiency, Efficiency_nom) | Alias( AVG(ILoad), ILOAD_Nom ) | Alias( AVG(Power(Q1)) , Power_Q1_Nom ) | Alias( AVG(Power(Q2)) , Power_Q2_Nom ) | Alias( Power(Line) , Power_Line_Nom ) | Alias( Power(Load) , Power_Load_Nom ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Nom ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Nominal) | SOURCE(INPUT:2, Nominal) | LOAD(OUTPUT:1, 35%) | Steady-State|Steady-State|Vin Nominal|35% | Alias( Efficiency, Efficiency_nom) | Alias( AVG(ILoad), ILOAD_Nom ) | Alias( AVG(Power(Q1)) , Power_Q1_Nom ) | Alias( AVG(Power(Q2)) , Power_Q2_Nom ) | Alias( Power(Line) , Power_Line_Nom ) | Alias( Power(Load) , Power_Load_Nom ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Nom ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Nominal) | SOURCE(INPUT:2, Nominal) | LOAD(OUTPUT:1, 40%) | Steady-State|Steady-State|Vin Nominal|40% | Alias( Efficiency, Efficiency_nom) | Alias( AVG(ILoad), ILOAD_Nom ) | Alias( AVG(Power(Q1)) , Power_Q1_Nom ) | Alias( AVG(Power(Q2)) , Power_Q2_Nom ) | Alias( Power(Line) , Power_Line_Nom ) | Alias( Power(Load) , Power_Load_Nom ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Nom ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Nominal) | SOURCE(INPUT:2, Nominal) | LOAD(OUTPUT:1, 50%) | Steady-State|Steady-State|Vin Nominal|50% | Alias( Efficiency, Efficiency_nom) | Alias( AVG(ILoad), ILOAD_Nom ) | Alias( AVG(Power(Q1)) , Power_Q1_Nom ) | Alias( AVG(Power(Q2)) , Power_Q2_Nom ) | Alias( Power(Line) , Power_Line_Nom ) | Alias( Power(Load) , Power_Load_Nom ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Nom ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Nominal) | SOURCE(INPUT:2, Nominal) | LOAD(OUTPUT:1, 60%) | Steady-State|Steady-State|Vin Nominal|60% | Alias( Efficiency, Efficiency_nom) | Alias( AVG(ILoad), ILOAD_Nom ) | Alias( AVG(Power(Q1)) , Power_Q1_Nom ) | Alias( AVG(Power(Q2)) , Power_Q2_Nom ) | Alias( Power(Line) , Power_Line_Nom ) | Alias( Power(Load) , Power_Load_Nom ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Nom ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Nominal) | SOURCE(INPUT:2, Nominal) | LOAD(OUTPUT:1, 70%) | Steady-State|Steady-State|Vin Nominal|70% | Alias( Efficiency, Efficiency_nom) | Alias( AVG(ILoad), ILOAD_Nom ) | Alias( AVG(Power(Q1)) , Power_Q1_Nom ) | Alias( AVG(Power(Q2)) , Power_Q2_Nom ) | Alias( Power(Line) , Power_Line_Nom ) | Alias( Power(Load) , Power_Load_Nom ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Nom ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Nominal) | SOURCE(INPUT:2, Nominal) | LOAD(OUTPUT:1, 80%) | Steady-State|Steady-State|Vin Nominal|80% | Alias( Efficiency, Efficiency_nom) | Alias( AVG(ILoad), ILOAD_Nom ) | Alias( AVG(Power(Q1)) , Power_Q1_Nom ) | Alias( AVG(Power(Q2)) , Power_Q2_Nom ) | Alias( Power(Line) , Power_Line_Nom ) | Alias( Power(Load) , Power_Load_Nom ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Nom ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Nominal) | SOURCE(INPUT:2, Nominal) | LOAD(OUTPUT:1, 90%) | Steady-State|Steady-State|Vin Nominal|90% | Alias( Efficiency, Efficiency_nom) | Alias( AVG(ILoad), ILOAD_Nom ) | Alias( AVG(Power(Q1)) , Power_Q1_Nom ) | Alias( AVG(Power(Q2)) , Power_Q2_Nom ) | Alias( Power(Line) , Power_Line_Nom ) | Alias( Power(Load) , Power_Load_Nom ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Nom ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Nominal) | SOURCE(INPUT:2, Nominal) | LOAD(OUTPUT:1, 100%) | Steady-State|Steady-State|Vin Nominal|100% | Alias( Efficiency, Efficiency_nom) | Alias( AVG(ILoad), ILOAD_Nom ) | Alias( AVG(Power(Q1)) , Power_Q1_Nom ) | Alias( AVG(Power(Q2)) , Power_Q2_Nom ) | Alias( Power(Line) , Power_Line_Nom ) | Alias( Power(Load) , Power_Load_Nom ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Nom ) | |

| *** | |||||||||||||

| Steady-State | Steady-State | SOURCE(INPUT:1, Maximum) | SOURCE(INPUT:2, Maximum) | LOAD(OUTPUT:1, 5%) | Steady-State|Steady-State|Vin Maximum|5% | Alias( Efficiency, Efficiency_Max) | Alias( AVG(ILoad), ILOAD_Max ) | Alias( AVG(Power(Q1)), Power_Q1_Max ) | Alias( AVG(Power(Q2)) , Power_Q2_Max ) | Alias( Power(Line) , Power_Line_Max ) | Alias( Power(Load) , Power_Load_Max ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Max ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Maximum) | SOURCE(INPUT:2, Maximum) | LOAD(OUTPUT:1, 10%) | Steady-State|Steady-State|Vin Maximum|10% | Alias( Efficiency, Efficiency_Max) | Alias( AVG(ILoad), ILOAD_Max ) | Alias( AVG(Power(Q1)), Power_Q1_Max ) | Alias( AVG(Power(Q2)) , Power_Q2_Max ) | Alias( Power(Line) , Power_Line_Max ) | Alias( Power(Load) , Power_Load_Max ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Max ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Maximum) | SOURCE(INPUT:2, Maximum) | LOAD(OUTPUT:1, 15%) | Steady-State|Steady-State|Vin Maximum|15% | Alias( Efficiency, Efficiency_Max) | Alias( AVG(ILoad), ILOAD_Max ) | Alias( AVG(Power(Q1)), Power_Q1_Max ) | Alias( AVG(Power(Q2)) , Power_Q2_Max ) | Alias( Power(Line) , Power_Line_Max ) | Alias( Power(Load) , Power_Load_Max ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Max ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Maximum) | SOURCE(INPUT:2, Maximum) | LOAD(OUTPUT:1, 20%) | Steady-State|Steady-State|Vin Maximum|20% | Alias( Efficiency, Efficiency_Max) | Alias( AVG(ILoad), ILOAD_Max ) | Alias( AVG(Power(Q1)), Power_Q1_Max ) | Alias( AVG(Power(Q2)) , Power_Q2_Max ) | Alias( Power(Line) , Power_Line_Max ) | Alias( Power(Load) , Power_Load_Max ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Max ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Maximum) | SOURCE(INPUT:2, Maximum) | LOAD(OUTPUT:1, 25%) | Steady-State|Steady-State|Vin Maximum|25% | Alias( Efficiency, Efficiency_Max) | Alias( AVG(ILoad), ILOAD_Max ) | Alias( AVG(Power(Q1)), Power_Q1_Max ) | Alias( AVG(Power(Q2)) , Power_Q2_Max ) | Alias( Power(Line) , Power_Line_Max ) | Alias( Power(Load) , Power_Load_Max ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Max ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Maximum) | SOURCE(INPUT:2, Maximum) | LOAD(OUTPUT:1, 30%) | Steady-State|Steady-State|Vin Maximum|30% | Alias( Efficiency, Efficiency_Max) | Alias( AVG(ILoad), ILOAD_Max ) | Alias( AVG(Power(Q1)), Power_Q1_Max ) | Alias( AVG(Power(Q2)) , Power_Q2_Max ) | Alias( Power(Line) , Power_Line_Max ) | Alias( Power(Load) , Power_Load_Max ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Max ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Maximum) | SOURCE(INPUT:2, Maximum) | LOAD(OUTPUT:1, 35%) | Steady-State|Steady-State|Vin Maximum|35% | Alias( Efficiency, Efficiency_Max) | Alias( AVG(ILoad), ILOAD_Max ) | Alias( AVG(Power(Q1)), Power_Q1_Max ) | Alias( AVG(Power(Q2)) , Power_Q2_Max ) | Alias( Power(Line) , Power_Line_Max ) | Alias( Power(Load) , Power_Load_Max ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Max ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Maximum) | SOURCE(INPUT:2, Maximum) | LOAD(OUTPUT:1, 40%) | Steady-State|Steady-State|Vin Maximum|40% | Alias( Efficiency, Efficiency_Max) | Alias( AVG(ILoad), ILOAD_Max ) | Alias( AVG(Power(Q1)), Power_Q1_Max ) | Alias( AVG(Power(Q2)) , Power_Q2_Max ) | Alias( Power(Line) , Power_Line_Max ) | Alias( Power(Load) , Power_Load_Max ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Max ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Maximum) | SOURCE(INPUT:2, Maximum) | LOAD(OUTPUT:1, 50%) | Steady-State|Steady-State|Vin Maximum|50% | Alias( Efficiency, Efficiency_Max) | Alias( AVG(ILoad), ILOAD_Max ) | Alias( AVG(Power(Q1)), Power_Q1_Max ) | Alias( AVG(Power(Q2)) , Power_Q2_Max ) | Alias( Power(Line) , Power_Line_Max ) | Alias( Power(Load) , Power_Load_Max ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Max ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Maximum) | SOURCE(INPUT:2, Maximum) | LOAD(OUTPUT:1, 60%) | Steady-State|Steady-State|Vin Maximum|60% | Alias( Efficiency, Efficiency_Max) | Alias( AVG(ILoad), ILOAD_Max ) | Alias( AVG(Power(Q1)), Power_Q1_Max ) | Alias( AVG(Power(Q2)) , Power_Q2_Max ) | Alias( Power(Line) , Power_Line_Max ) | Alias( Power(Load) , Power_Load_Max ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Max ) | |

| *** | |||||||||||||

| Steady-State | Steady-State | SOURCE(INPUT:1, Maximum) | SOURCE(INPUT:2, Maximum) | LOAD(OUTPUT:1, 70%) | Steady-State|Steady-State|Vin Maximum|70% | Alias( Efficiency, Efficiency_Max) | Alias( AVG(ILoad), ILOAD_Max ) | Alias( AVG(Power(Q1)), Power_Q1_Max ) | Alias( AVG(Power(Q2)) , Power_Q2_Max ) | Alias( Power(Line) , Power_Line_Max ) | Alias( Power(Load) , Power_Load_Max ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Max ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Maximum) | SOURCE(INPUT:2, Maximum) | LOAD(OUTPUT:1, 80%) | Steady-State|Steady-State|Vin Maximum|80% | Alias( Efficiency, Efficiency_Max) | Alias( AVG(ILoad), ILOAD_Max ) | Alias( AVG(Power(Q1)), Power_Q1_Max ) | Alias( AVG(Power(Q2)) , Power_Q2_Max ) | Alias( Power(Line) , Power_Line_Max ) | Alias( Power(Load) , Power_Load_Max ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Max ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Maximum) | SOURCE(INPUT:2, Maximum) | LOAD(OUTPUT:1, 90%) | Steady-State|Steady-State|Vin Maximum|90% | Alias( Efficiency, Efficiency_Max) | Alias( AVG(ILoad), ILOAD_Max ) | Alias( AVG(Power(Q1)), Power_Q1_Max ) | Alias( AVG(Power(Q2)) , Power_Q2_Max ) | Alias( Power(Line) , Power_Line_Max ) | Alias( Power(Load) , Power_Load_Max ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Max ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Maximum) | SOURCE(INPUT:2, Maximum) | LOAD(OUTPUT:1, 100%) | Steady-State|Steady-State|Vin Maximum|100% | Alias( Efficiency, Efficiency_Max) | Alias( AVG(ILoad), ILOAD_Max ) | Alias( AVG(Power(Q1)), Power_Q1_Max ) | Alias( AVG(Power(Q2)) , Power_Q2_Max ) | Alias( Power(Line) , Power_Line_Max ) | Alias( Power(Load) , Power_Load_Max ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Max ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Minimum) | SOURCE(INPUT:2, Minimum) | LOAD(OUTPUT:1, 5%) | Steady-State|Steady-State|Vin Minimum|5% | Alias( Efficiency, Efficiency_Min) | Alias( AVG(ILoad), ILOAD_Min ) | Alias( AVG(Power(Q1)) , Power_Q1_Min ) | Alias( AVG(Power(Q2)) , Power_Q2_Min ) | Alias( Power(Line) , Power_Line_Min ) | Alias( Power(Load) , Power_Load_Min ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Min ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Minimum) | SOURCE(INPUT:2, Minimum) | LOAD(OUTPUT:1, 10%) | Steady-State|Steady-State|Vin Minimum|10% | Alias( Efficiency, Efficiency_Min) | Alias( AVG(ILoad), ILOAD_Min ) | Alias( AVG(Power(Q1)) , Power_Q1_Min ) | Alias( AVG(Power(Q2)) , Power_Q2_Min ) | Alias( Power(Line) , Power_Line_Min ) | Alias( Power(Load) , Power_Load_Min ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Min ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Minimum) | SOURCE(INPUT:2, Minimum) | LOAD(OUTPUT:1, 15%) | Steady-State|Steady-State|Vin Minimum|15% | Alias( Efficiency, Efficiency_Min) | Alias( AVG(ILoad), ILOAD_Min ) | Alias( AVG(Power(Q1)) , Power_Q1_Min ) | Alias( AVG(Power(Q2)) , Power_Q2_Min ) | Alias( Power(Line) , Power_Line_Min ) | Alias( Power(Load) , Power_Load_Min ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Min ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Minimum) | SOURCE(INPUT:2, Minimum) | LOAD(OUTPUT:1, 20%) | Steady-State|Steady-State|Vin Minimum|20% | Alias( Efficiency, Efficiency_Min) | Alias( AVG(ILoad), ILOAD_Min ) | Alias( AVG(Power(Q1)) , Power_Q1_Min ) | Alias( AVG(Power(Q2)) , Power_Q2_Min ) | Alias( Power(Line) , Power_Line_Min ) | Alias( Power(Load) , Power_Load_Min ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Min ) | |

| *** | |||||||||||||

| Steady-State | Steady-State | SOURCE(INPUT:1, Minimum) | SOURCE(INPUT:2, Minimum) | LOAD(OUTPUT:1, 25%) | Steady-State|Steady-State|Vin Minimum|25% | Alias( Efficiency, Efficiency_Min) | Alias( AVG(ILoad), ILOAD_Min ) | Alias( AVG(Power(Q1)) , Power_Q1_Min ) | Alias( AVG(Power(Q2)) , Power_Q2_Min ) | Alias( Power(Line) , Power_Line_Min ) | Alias( Power(Load) , Power_Load_Min ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Min ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Minimum) | SOURCE(INPUT:2, Minimum) | LOAD(OUTPUT:1, 30%) | Steady-State|Steady-State|Vin Minimum|30% | Alias( Efficiency, Efficiency_Min) | Alias( AVG(ILoad), ILOAD_Min ) | Alias( AVG(Power(Q1)) , Power_Q1_Min ) | Alias( AVG(Power(Q2)) , Power_Q2_Min ) | Alias( Power(Line) , Power_Line_Min ) | Alias( Power(Load) , Power_Load_Min ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Min ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Minimum) | SOURCE(INPUT:2, Minimum) | LOAD(OUTPUT:1, 35%) | Steady-State|Steady-State|Vin Minimum|35% | Alias( Efficiency, Efficiency_Min) | Alias( AVG(ILoad), ILOAD_Min ) | Alias( AVG(Power(Q1)) , Power_Q1_Min ) | Alias( AVG(Power(Q2)) , Power_Q2_Min ) | Alias( Power(Line) , Power_Line_Min ) | Alias( Power(Load) , Power_Load_Min ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Min ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Minimum) | SOURCE(INPUT:2, Minimum) | LOAD(OUTPUT:1, 40%) | Steady-State|Steady-State|Vin Minimum|40% | Alias( Efficiency, Efficiency_Min) | Alias( AVG(ILoad), ILOAD_Min ) | Alias( AVG(Power(Q1)) , Power_Q1_Min ) | Alias( AVG(Power(Q2)) , Power_Q2_Min ) | Alias( Power(Line) , Power_Line_Min ) | Alias( Power(Load) , Power_Load_Min ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Min ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Minimum) | SOURCE(INPUT:2, Minimum) | LOAD(OUTPUT:1, 50%) | Steady-State|Steady-State|Vin Minimum|50% | Alias( Efficiency, Efficiency_Min) | Alias( AVG(ILoad), ILOAD_Min ) | Alias( AVG(Power(Q1)) , Power_Q1_Min ) | Alias( AVG(Power(Q2)) , Power_Q2_Min ) | Alias( Power(Line) , Power_Line_Min ) | Alias( Power(Load) , Power_Load_Min ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Min ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Minimum) | SOURCE(INPUT:2, Minimum) | LOAD(OUTPUT:1, 60%) | Steady-State|Steady-State|Vin Minimum|60% | Alias( Efficiency, Efficiency_Min) | Alias( AVG(ILoad), ILOAD_Min ) | Alias( AVG(Power(Q1)) , Power_Q1_Min ) | Alias( AVG(Power(Q2)) , Power_Q2_Min ) | Alias( Power(Line) , Power_Line_Min ) | Alias( Power(Load) , Power_Load_Min ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Min ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Minimum) | SOURCE(INPUT:2, Minimum) | LOAD(OUTPUT:1, 70%) | Steady-State|Steady-State|Vin Minimum|70% | Alias( Efficiency, Efficiency_Min) | Alias( AVG(ILoad), ILOAD_Min ) | Alias( AVG(Power(Q1)) , Power_Q1_Min ) | Alias( AVG(Power(Q2)) , Power_Q2_Min ) | Alias( Power(Line) , Power_Line_Min ) | Alias( Power(Load) , Power_Load_Min ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Min ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Minimum) | SOURCE(INPUT:2, Minimum) | LOAD(OUTPUT:1, 80%) | Steady-State|Steady-State|Vin Minimum|80% | Alias( Efficiency, Efficiency_Min) | Alias( AVG(ILoad), ILOAD_Min ) | Alias( AVG(Power(Q1)) , Power_Q1_Min ) | Alias( AVG(Power(Q2)) , Power_Q2_Min ) | Alias( Power(Line) , Power_Line_Min ) | Alias( Power(Load) , Power_Load_Min ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Min ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Minimum) | SOURCE(INPUT:2, Minimum) | LOAD(OUTPUT:1, 90%) | Steady-State|Steady-State|Vin Minimum|90% | Alias( Efficiency, Efficiency_Min) | Alias( AVG(ILoad), ILOAD_Min ) | Alias( AVG(Power(Q1)) , Power_Q1_Min ) | Alias( AVG(Power(Q2)) , Power_Q2_Min ) | Alias( Power(Line) , Power_Line_Min ) | Alias( Power(Load) , Power_Load_Min ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Min ) | |

| Steady-State | Steady-State | SOURCE(INPUT:1, Minimum) | SOURCE(INPUT:2, Minimum) | LOAD(OUTPUT:1, 100%) | Steady-State|Steady-State|Vin Minimum|100% | Alias( Efficiency, Efficiency_Min) | Alias( AVG(ILoad), ILOAD_Min ) | Alias( AVG(Power(Q1)) , Power_Q1_Min ) | Alias( AVG(Power(Q2)) , Power_Q2_Min ) | Alias( Power(Line) , Power_Line_Min ) | Alias( Power(Load) , Power_Load_Min ) | Alias( Power(Gate_Drive) , Power_Gate_Drive_Min ) | |

| NoSimulation | Steady-State|Generate Efficiency Curves | ..\scripts\8.1_efficiency_and_powerloss_post_process.sxscr | |||||||||||

After running 8.1_efficiency_and_powerloss.testplan on the 8.1_Sync Buck Efficiency.sxsch schematic, the overview test report shows five graphs:

- Efficiency

- Power losses in the high-side MOSFET

- Power losses in the low-side MOSFET

- High-side gate-drive power

- Remaining power

Applying this testplan to a new schematic:

- As mentioned previously, the source, load, and probe names on the schematic must match the names in the testplan Alias functions.

- To make these names match, you may change either the schematic or the testplan; the choice is up to you.

- This testplan expects the schematic to have two input sources. If you attempt to run this testplan on a schematic with one input source, DVM produces an error message and aborts the test run.