Rapid digital prototyping at the concept stage, thorough verification of the synthesizable digital design in the full analog application circuit before committing to silicon.

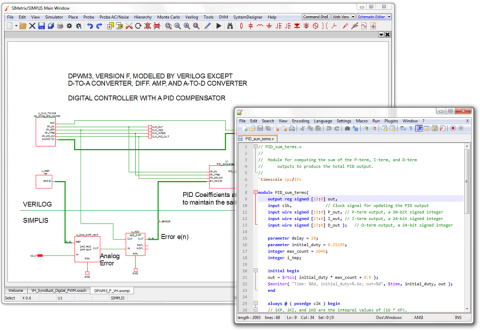

The new SIMPLIS Verilog-HDL Co-simulation module enables the fast, industry-verified SIMPLIS analog simulation engine to run in parallel with a Verilog-HDL simulation engine to permit users to analyze a behavioral or gate-level digital IC design operating in an actual analog application circuit instead of merely pairing it with an artificial input stimulus test bench. Designers interested in exploring new digital control algorithms can use behavioral Verilog-HDL syntax to get their ideas to the testing stage without having to delve into gate-level design. At verification time, the designer can test the performance of the synthesizable Verilog-HDL design against the original application circuit specifications before submitting for silicon layout.

SIMetrix/SIMPLIS Pro VH and SIMetrix/SIMPLIS Elite VH ship with the following versions of the open-source Icarus Verilog simulator:

- v0.9.1 (stable)

- v0.9.7 (stable)

- v10.1.1 (stable)

- 20150105 (snapshot)

SIMetrix/SIMPLIS Pro VH and SIMetrix/SIMPLIS Elite VH also support Siemens' ModelSim (former Mentor Graphics' ModelSim) versions 10.4 and later.