StepLoad() Test Objective

The purpose of the StepLoad() test is to verify that the output voltage is within regulation when the load current is ramped between the initial and final current values. The input is configured as a DC Input Source, and the output is configured as a Ramp Load. The initial current is modeled as resistive and the actual load step is implemented with a current source. The initial and final current values are passed as arguments to the StepLoad() function in the testplan. The built-in testplans support both a load step increase and a load step decrease.

Both a POP and transient analysis are used in the StepLoad() test.

- The POP simulation finds the steady-state operating point of the converter at the initial current.

- The transient simulation starts at the initial conditions found during the POP

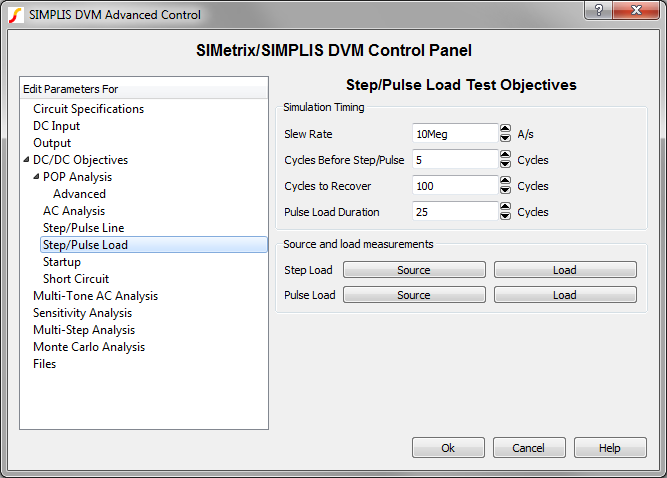

simulation. The timing for the transient simulation is taken from the Circuit Specifications page and the Step/Pulse Load page of the Full Power Assist DVM control symbol. The Pulse Load page is shown below.

The test report includes source and load graphs as well as the following scalar values which are defined in the Measured Scalar Values section below:

- Switching frequency

- Output voltage recovery time

- Overshoot and Undershoot voltages.

In this topic:

Testplan Syntax

The StepLoad() function has the following syntax with the arguments described in the table below:

StepLoad(REF, ISTART, IFINAL) StepLoad(REF, ISTART, IFINAL, OPTIONAL_PARAMETER_STRING)

| Argument | Range | Description |

| REF | n/a | The actual reference designator of the DVM Load or the generic syntax of OUTPUT:n where n is an integer indicating a position in the list of DVM loads. |

| I START | min:0 | The starting current for the load. This can be a numeric value or a symbolic value, such as a percentage of full load. |

| I FINAL | min:0 | The final current for the load. This can be a numeric value or a symbolic value, such as a percentage of full load. |

| OPTIONAL_PARAMETER_STRING | n/a | Parameter string with a combination of one

or more timing parameters:

|

parameter_name1=parameter_value1 parameter_name2=parameter_value2The order of the parameter key-value pairs does not matter.

Simulation Timing

DVM sets the timing parameters for the StepLoad() test objective based on values that you enter on the following two tabs in the DVM Full Power Assist control symbol:

- Step/Pulse Load page: Cycles Before Event, Cycles to Recover, and Slew Rate

- Circuit Specifications page: Switching Frequency

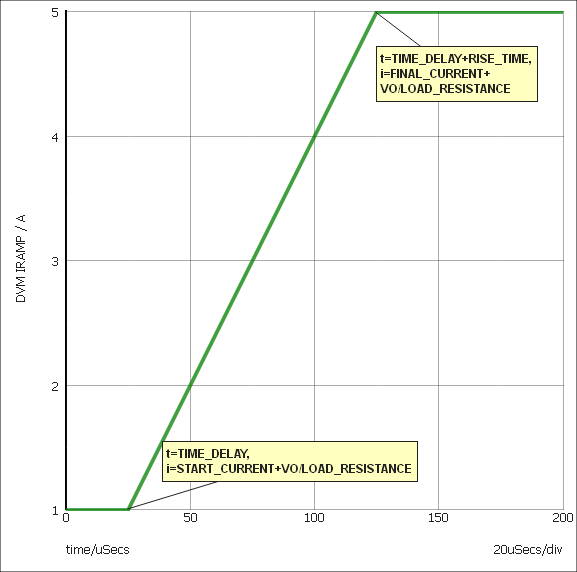

The time delay, rise time, and the simulation stop time are determined by these calculations:

\[ \text{TIME_DELAY} = \frac{\text{CYCLES_BEFORE_EVENT}}{\text{SWITCHING_FREQUENCY}} \]

\[ \text{RISE_TIME} = \frac{ abs \left( I_{FINAL}-I_{START} \right)}{\text{SLEW_RATE}} \]

\[ \text{STOP_TIME} = \text{TIME_DELAY} + \text{RISE_TIME} + \frac{\text{CYCLES_TO_RECOVER}}{\text{SWITCHING_FREQUENCY}}\]

The output current ramp/step timing is annotated on the graph below:

| Annotation | Value |

| X0 | TIME_DELAY |

| X1 | TIME_DELAY + RISE_TIME |

| Y0 | ISTART (see note below) |

| Y1 | IFINAL (see note below) |

Source and Load Subcircuit Configuration

The StepLoad() test objective sets the source and load subcircuits to the following:

| Source | Load |

| DC Input Source | Ramp Load |

Loads other than the output under test are set to the Resistive Load. All other sources are set to the DC Input Source.

Measured Scalar Values

The StepLoad() test objective measures the following scalar values,where {load_name} and {src_name} are replaced by the actual load name source name:

| Scalar Name | Description | ||||||||||

| sw_freq | A number which represents the converter switching frequency. This scalar is generated from a fixed probe with curve label DVM Frequency. For more information, see Measuring the Switching Frequency. | ||||||||||

| vout{n}_recovery_time | The number {n}

in the scalar name is an integer indicating a position in the

list of DVM loads.

The three possible return values are the following:

|

||||||||||

|

The Average, Minimum, Maximum, RMS and Peak-to-Peak values for each load voltage and current taken over the entire simulation time window. | ||||||||||

|

The Average, Minimum, Maximum, RMS and Peak-to-Peak values for each source voltage and current taken over the entire simulation time window. |

Measured Specification Values

In the following table, {load_name} is the name assigned to each load. The default value is LOAD. DVM forces each load name to be unique so that the scalar and specification values for each load are unique.

| Specification Name | PASS/FAIL Criteria |

| Min_V{load_name} | The minimum value of the output voltage during the simulation time is greater that the minimum specification value. |

| Max_V{load_name} | The maximum value of the output during the simulation time is less than the maximum specification value. |

| Overshoot_V{load_name} | The maximum value of the output during the simulation time is less than the maximum overshoot specification value. |

| Undershoot_V{load_name} | The minimum value of the output during the simulation time is greater than the minimum undershoot specification value. |

Testplan Example

The StepLoad() test objective is used in several built-in testplans. Shown below is a test from the DC/DC 1 input/1 output testplan. This test configures the load to step from the 50% full load value to the 100% full load value. The full load value is defined on the Output page of the Full Power Assist DVM control symbol.

| *?@ Analysis | Objective | Source | Load | Label |

| Transient | StepLoad(OUTPUT:1, 50%, 100%) | Source(INPUT:1, Nominal) | Transient|Step Load|Vin Nominal|50% Load to 100% Load |

Optional Parameter String

The following StepLoad() test objective uses the OPTIONAL_PARAMETER_STRING argument to set the output load to step between the Light and 100% symbolic values and sets the ramp time delay to 25us and the ramp rise time to 100us.

StepLoad(OUTPUT:1, 50%, 100%, TIME_DELAY=25u RISE_TIME=100u)

Test Report

You can view the complete test report in a new browser window here: StepLoad() Test Report. Below is an interactive link to the same test report.